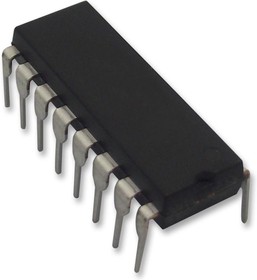

Характеристики

SN74HC166N, ИР10The SN74HC166N is a 8-bit parallel-load Shift Register features gated clock (CLK, CLK INH) inputs and an overriding clear (CLR) input. The parallel-in or serial-in modes are established by the shift/load (SH/LD) input. When high, SH/LD enables the serial (SER) data input and couples the eight flip-flops for serial shifting with each CLK pulse. When low, the parallel (broadside) data inputs are enabled and synchronous loading occurs on the next clock pulse. During parallel loading, serial data flow is inhibited. clocking is accomplished on the low-to-high-level edge of CLK through a 2-input positive-NOR gate permitting one input to be used as a clock-enable or clock-inhibit function. Holding either CLK or CLK INH high inhibits clocking, holding either low enables the other clock input. This allows the system clock to be free running and the register can be stopped on command with the other clock input. CLK INH should be changed to the high level only when CLK is high.

• Outputs can drive up to 10 LSTTL loads

• Typical tpd = 13ns

• Synchronous load

• Direct overriding clear

• Parallel-to-serial conversion

• 80µA Maximum low power consumption

• ±4mA Output drive at 5V

• 1µA Maximum low input current

Микросхемы / Логические микросхемы / Микросхемы ТТЛ (серия 74)

Корпус: 16-PDIP, инфо: Логический элемент ТТЛ Регистр сдвиговый 8 бит Параллельный вход, параллельный выход КМОП кристалл, примечание: ИР10

Личный кабинет

Личный кабинет

Загрузка

Загрузка